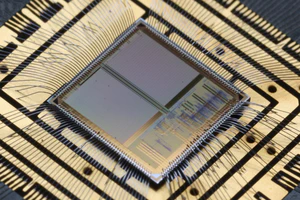

The Spikey chip is an accelerated spiking neuromorphic system integrating 384 integrate-and-fire neurons, 98k plastic synapses, and event routing. It enables fast emulation of complex neural dynamics and exploration of STDP-type synaptic plasticity.

The Spikey accelerated neuromorphic system is an integrated circuit architecture for emulating biologically-inspired spiking neural networks.

It was developed by researchers at the Heidelberg University.

Key features of the Spikey system include:

System Architecture

- Single-chip ASIC integrating a custom analog core with 384 neuron circuits, 98k plastic synapses, analog parameter storage, and an event routing network

- Synapses support STDP-type long-term and STP-type short-term plasticity.

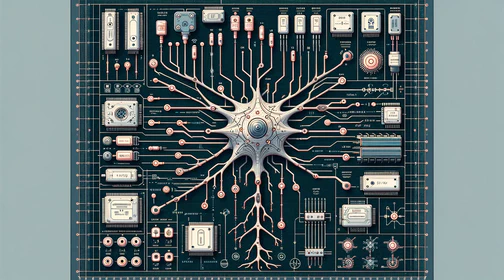

Neural and Synapse Circuits

- Implements the Leaky Integrate-and-Fire (LIF) neuron model with individually configurable model parameters

- On-chip synapse correlation and plasticity measurement enables programmable spike-timing dependent plasticity

Applications and Experiments

- Accelerated (50,000–100,000-fold compared to biological real time) emulation of complex spiking neuron dynamics

- Exploration of synaptic plasticity models and critical network dynamics at biological timescales

The accelerated operation and flexible architecture facilitate applications in computational neuroscience research.

Related publications

| Date | Title | Authors | Venue/Source |

|---|---|---|---|

| February 2013 | Six networks on a universal neuromorphic computing substrate | Thomas Pfeil, Andreas Grübl, Sebastian Jeltsch, Eric Müller, Paul Müller, Mihai A. Petrovici, Michael Schmuker, Daniel Brüderle, Johannes Schemmel, Karlheinz Meier | Frontiers in Neuroscience (Neuromorphic Engineering) |

| July 2012 | Is a 4-bit synaptic weight resolution enough? – constraints on enabling spike-timing dependent plasticity in neuromorphic hardware | Thomas Pfeil, Tobias C. Potjans, Sven Schrader, Wiebke Potjans, Johannes Schemmel, Markus Diesmann, Karlheinz Meier | Frontiers in Neuroscience (Neuromorphic Engineering) |

| June 2009 | Establishing a Novel Modeling Tool: a Python-based Interface for a Neuromorphic Hardware System | Daniel Brüderle, Eric Müller, Andrew Davison, Eilif Muller, Johannes Schemmel, Karlheinz Meier | Frontiers Neuroinformatics |

| June 2007 | Modeling Synaptic Plasticity within Networks of Highly Accelerated I&F Neurons | Johannes Schemmel, Daniel Bruderle, Karlheinz Meier, Boris Ostendorf | 2007 IEEE International Symposium on Circuits and Systems (ISCAS) |

| July 2006 | Implementing Synaptic Plasticity in a VLSI Spiking Neural Network Model | Johannes Schemmel, Andreas Grübl, Karlheinz Meier, Eilif Mueller | 2006 IEEE International Joint Conference on Neural Network (IJCNN) |

Help Us Improve this Guide

Our hardware guide is community-maintained. If you know of a chip we should add, see an error, or have updated information, please let us know by opening an issue on our GitHub repository.